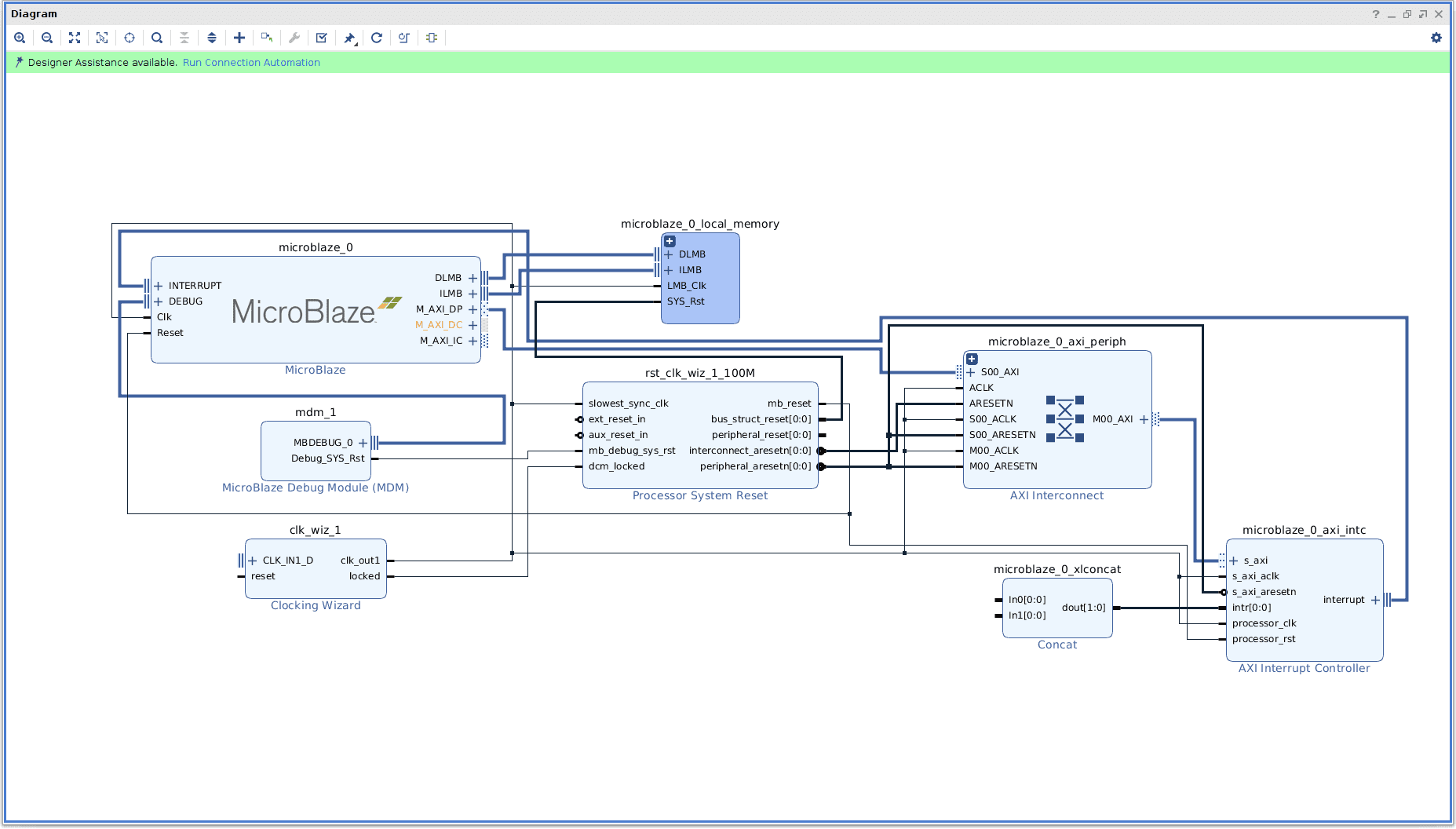

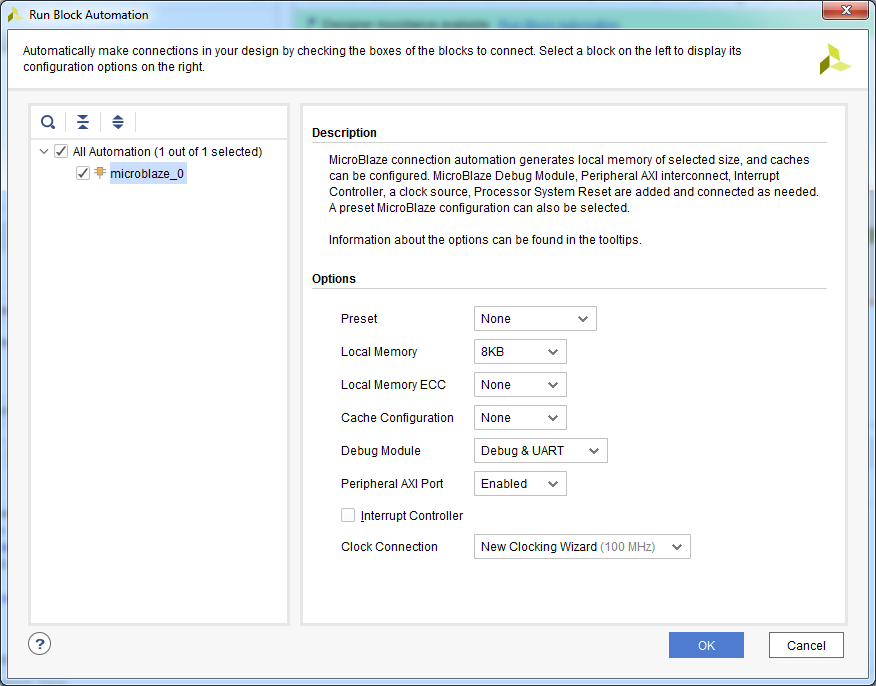

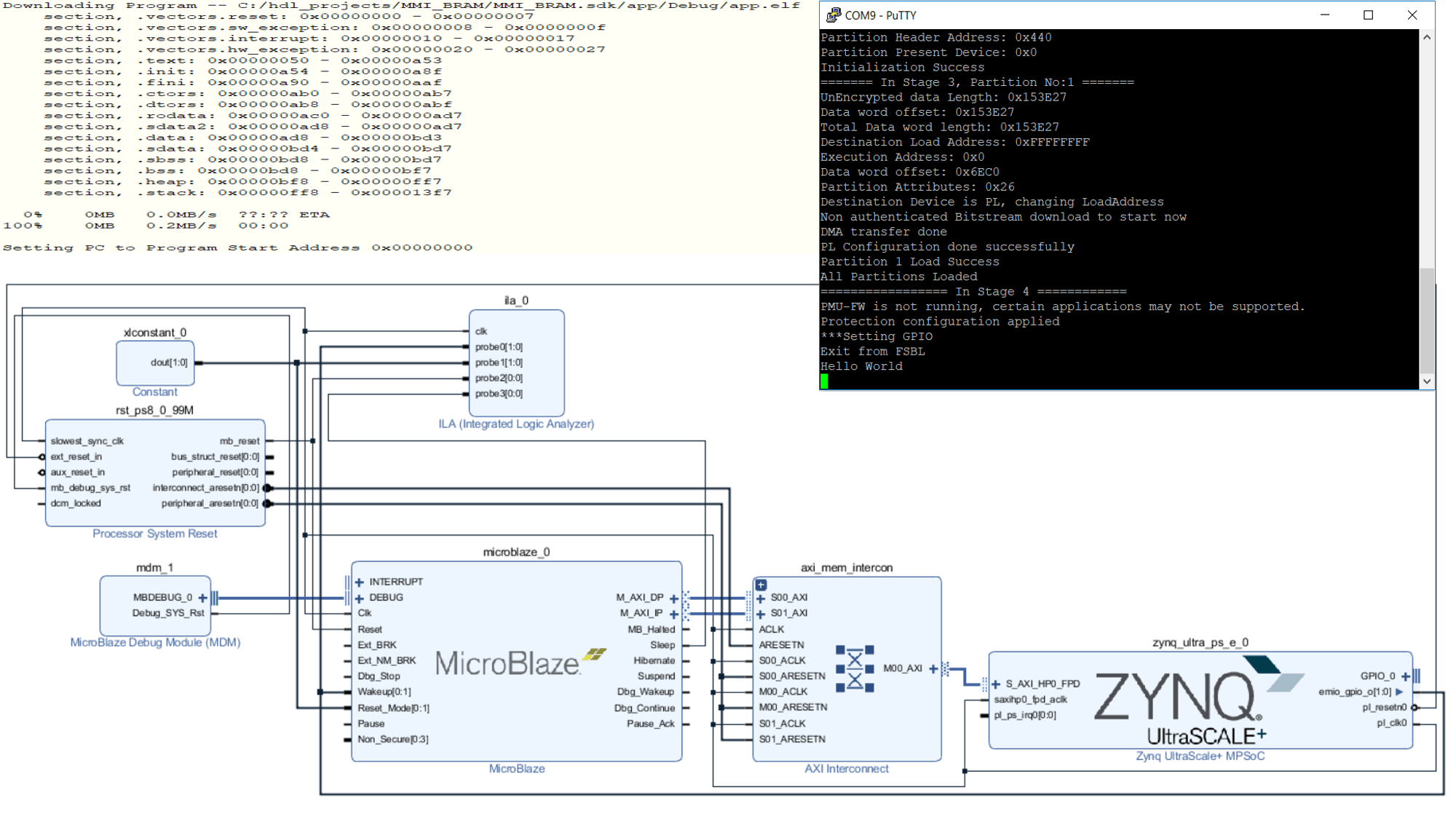

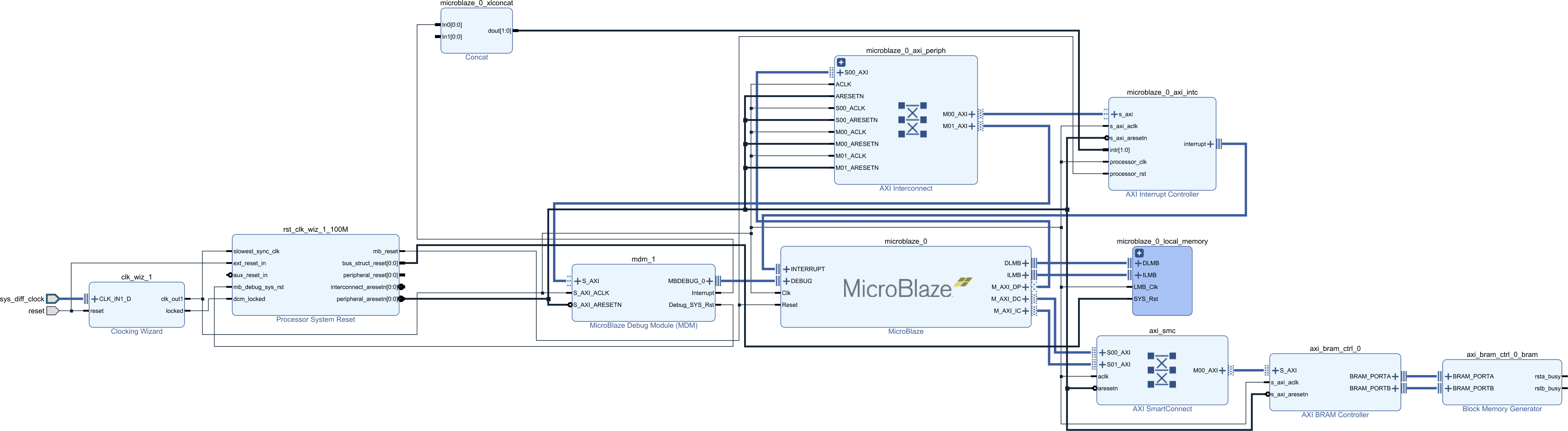

How can we use Ultraram effectively as local memory for Microblaze soft processor? Our FPGA device is XCVU3P. We want to use maximum possible on chip memory as local memory for Microblaze.

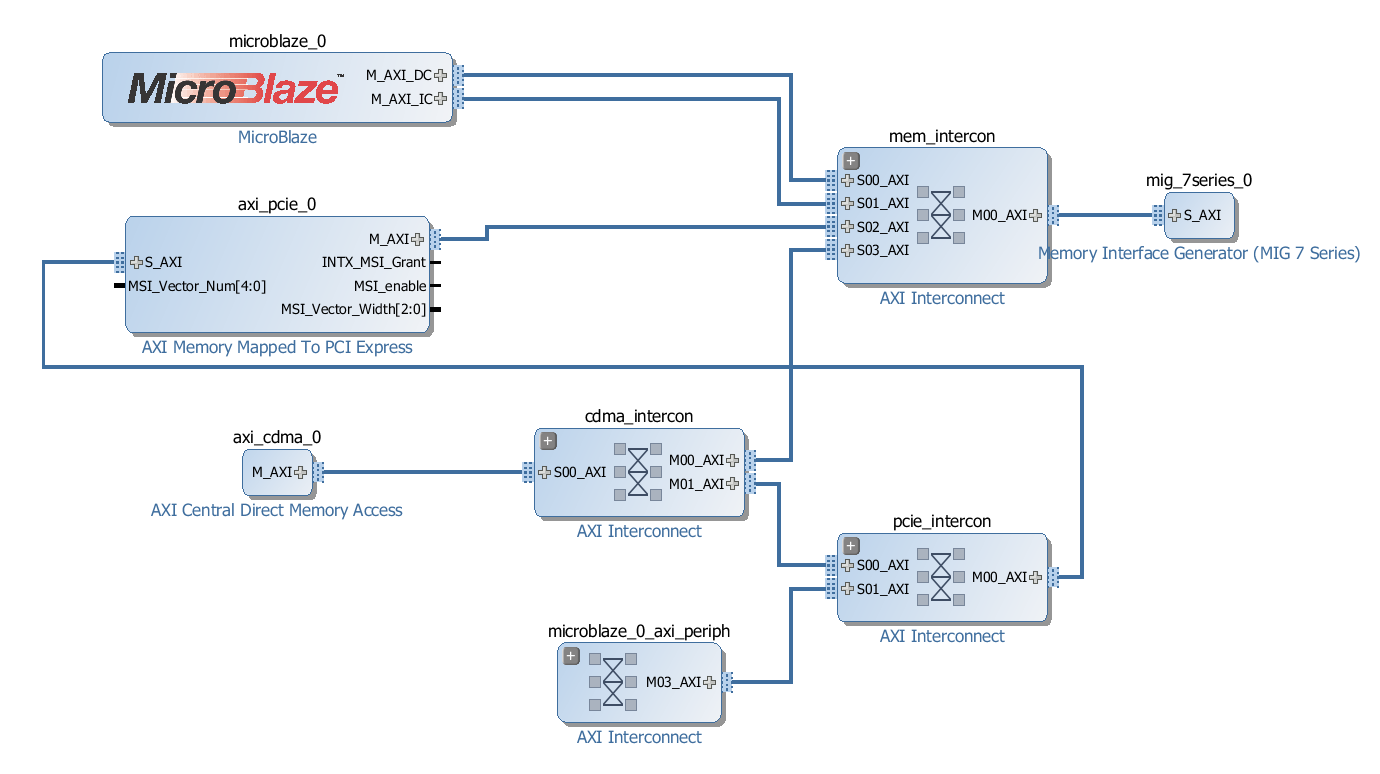

Multiprocessor based on shared memory/bus Fig 2 presents the second... | Download Scientific Diagram

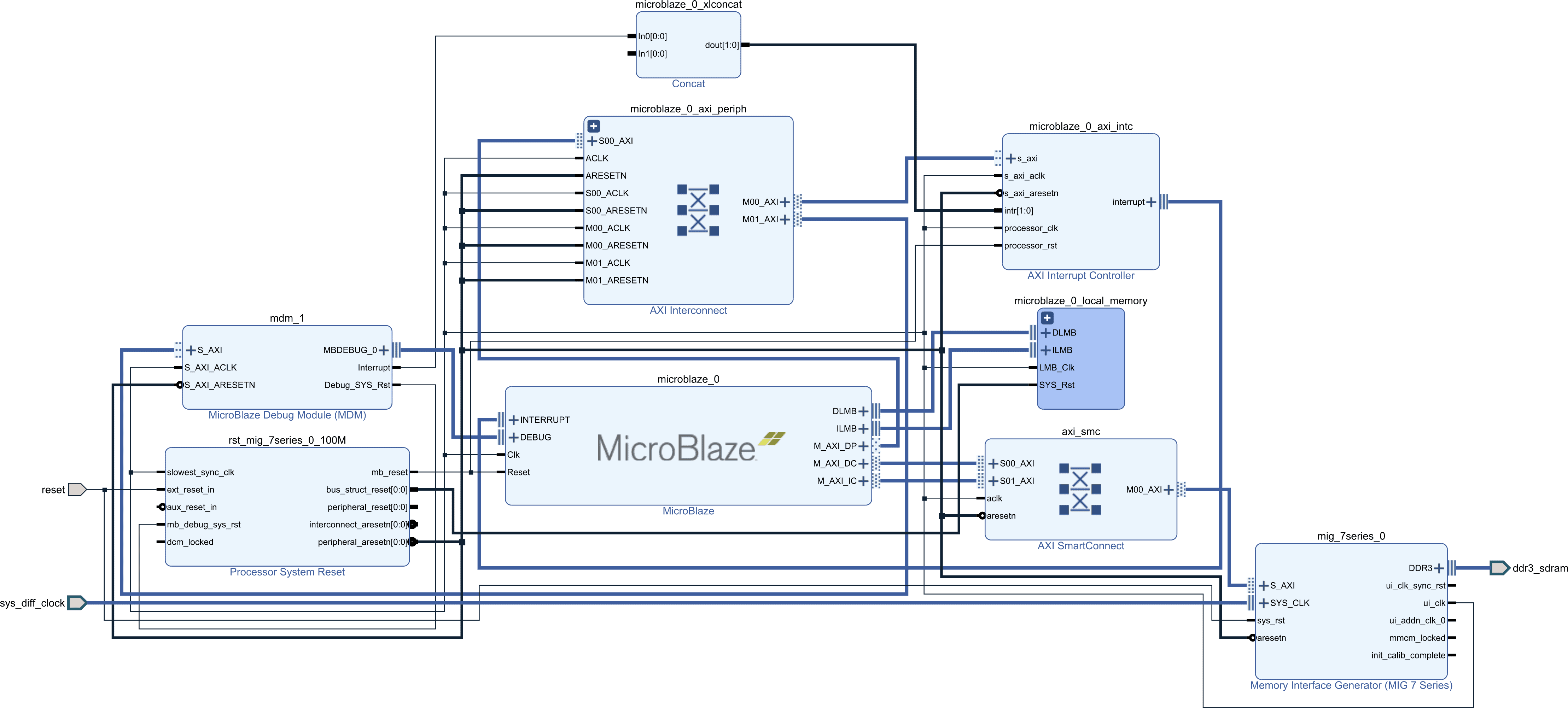

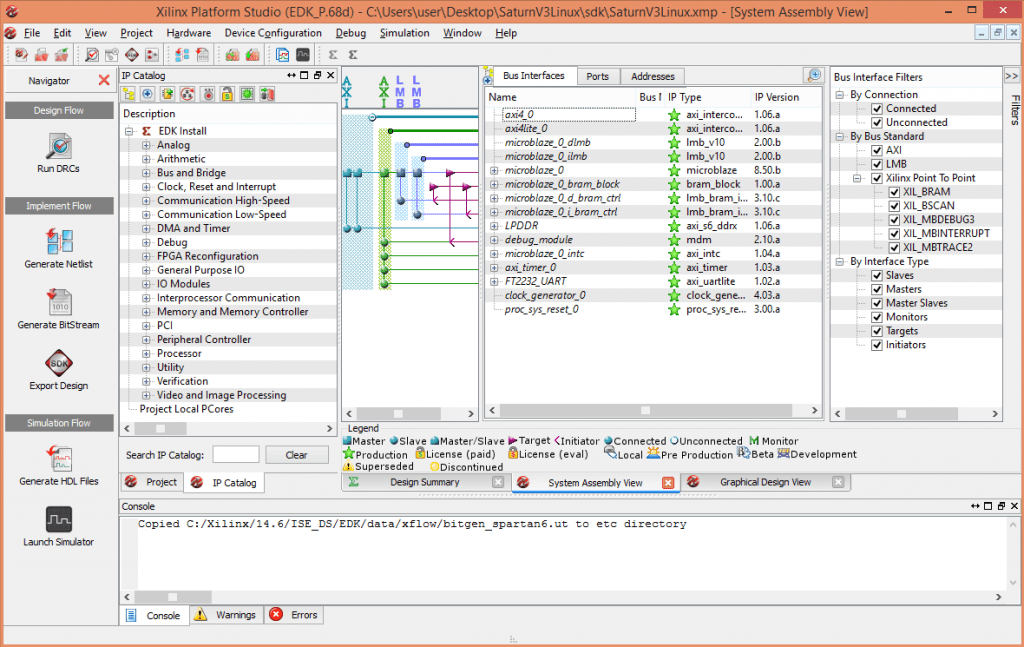

Creating Xilinx EDK test project for Saturn – Your first Microblaze processor based embedded design | Numato Lab Help Center